# An Improved Analytical AC Large-Signal Model for the GaAs MESFET

ASHER MADJAR, SENIOR MEMBER, IEEE

**Abstract** — Currently, the analysis of nonlinear microwave networks is a topic of much research effort and has produced many efficient and useful algorithms. To apply these algorithms, it is necessary to use an efficient model for each nonlinear device used. The modeling of MESFET's has been dealt with quite extensively in recent years, including a continuous effort by the author. In a recent publication, an efficient analytical model was presented. In the present paper, an improved model is described. The new model is basically the same as the previous one, except that a better expression is used for the conduction current calculation. The accuracy and applicability of the model are demonstrated by a set of simulation results and by comparison to measurement.

## I. INTRODUCTION

**I**N RECENT YEARS the analysis of microwave nonlinear networks has been of great interest, and much research effort has been devoted to it, resulting in efficient analysis methods. Some commercial computer programs are already available, and more are expected in the near future. References [1]–[7] are examples of some of the recent publications on this topic.

Obviously, the GaAs MESFET is a useful microwave device, so it is important to have an efficient and accurate model for it. The author has developed in the past a field-theory-based model [8], [9], which relates the device physics and geometry to its electrical performance. Recently, a fully analytical approximation of the above model has been developed and published [10]. The above analytical model has been used extensively for simulation of amplifiers, mixers, frequency multipliers, etc., using the harmonic balance technique. As a result, some improvements to the above model are presented here. The improved model allows better correlation between simulated and measured performance. In Section II the improved model is presented and an accuracy evaluation involving the comparison of simulated and measured performance is described in Section III.

## II. THE IMPROVED ANALYTICAL MODEL

### *A. General*

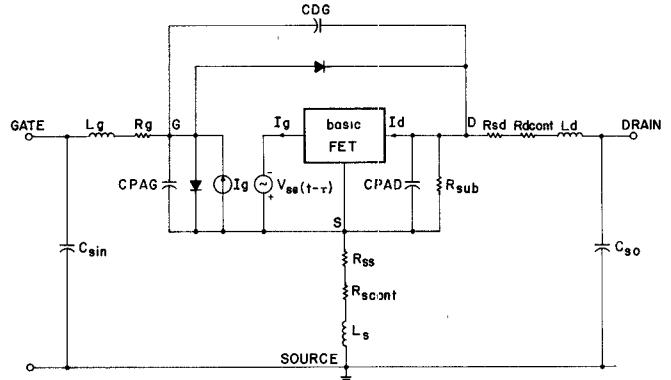

The MESFET large-signal model is presented in Fig. 1. This figure is the same as in [10], and the description of the various elements of the network is given there, as well as in

Manuscript received October 27, 1988; revised March 7, 1989.

The author is with the Technion—Israel Institute of Technology, Haifa, Israel.

IEEE Log Number 8929894.

Fig. 1. Complete MESFET network.

[8] and [9] with a modification by Green [11]. The box labeled “basic FET” in Fig. 1 represents the active nonlinear portion of the device. This portion is the main part of the device and the most difficult to simulate accurately. The passive parasitic components can be either calculated from the device geometry by existing field-theory-based models or measured in a procedure described by Curtice [12]. The nonlinear portion, however, is best characterized by mathematical expressions:

$$I_g(t) = \text{GVSG} \frac{dV_{SG}(t-\tau)}{dt} + \text{GVDS} \frac{dV_{DS}(t)}{dt} \quad (1)$$

$$I_D(t) = I_{\text{con}} + \text{DVSG} \frac{dV_{SG}(t-r)}{dt} + \text{DVDS} \frac{dV_{DS}(t)}{dt} \quad (2)$$

where  $I_{\text{con}}$  is the drain-source conduction current. The other four parameters are capacitive coefficients representing the displacement current. The five variables are functions of the internal port voltages:  $V_{SG}(t - \tau)$ ,  $V_{DS}(t)$ . This representation ((1) and (2)) is maintained over the entire dynamic range, including forward and avalanche conduction. This does not introduce an error, since the "basic FET" is practically shorted by the diodes when conduction occurs. Analytical expressions for the above five functions are presented in [10] in full detail in a form suitable for direct implementation by the reader. In this paper we present improved expressions for  $I_{\text{con}}$ , which better simulate this parameter. The four capacitive coefficients have not been changed, and they can be calculated by the expressions in [10].

### B. The New Expressions for $I_{\text{con}}$

The improved expression for  $I_{\text{con}}$  is

$$I_{\text{con}} = I_S (1 + mV_{DS}) \tanh(V_{DS}/V_S) \quad (1)$$

where  $I_S$ ,  $m$ , and  $V_S$  are functions of  $V_{SG}$ .

The physical meaning and expressions for the above functions are outlined below.  $I_S$  is the saturation current (same as  $I_{\text{sat}}$  in [10]). In the "old" model  $I_{\text{sat}}$  is calculated by expressions (5) in [10]. A better approximation has been derived as follows:

$$I_S = \begin{cases} I_{\text{ON}}, & V_{SG} < -V_F \\ A_1 V_{SG}^3 + A_2 V_{SG}^2 - g_{m0} V_{SG} + I_{DSS}, & -V_F \leq V_{SG} < 0 \\ A_3 V_{SG}^2 - g_{m0} V_{SG} + I_{DSS}, & 0 \leq V_{SG} < V_{\text{gds}} \\ A_4 V_{SG}^3 + A_5 V_{SG}^2 + A_6 V_{SG} + A_7, & V_{\text{gds}} < V_{SG} < V_{\text{cut}} \\ 0, & V_{\text{cut}} \leq V_{SG} \end{cases} \quad (2)$$

where

$$A_1 = \frac{2(I_{\text{ON}} - I_{DSS})}{V_F^3} - \frac{g_{m0}}{V_F^2}$$

$$A_2 = \frac{3(I_{\text{ON}} - I_{DSS})}{V_F^2} - \frac{2g_{m0}}{V_F} \quad (3)$$

$$A_3 = \frac{I_{DSm} - I_{DSS} + g_{m0} V_{\text{gds}}}{V_{\text{gds}}^2} \quad (4)$$

$$A_4 = \frac{1}{(V_{\text{cut}} - V_{\text{gds}})^2} \left[ \frac{2I_{DSm}}{V_{\text{cut}} - V_{\text{gds}}} + g_{m0} - 2 \frac{I_{DSS} - I_{DSm}}{V_{\text{gds}}} \right] \quad (5)$$

$$A_5 = \frac{I_{DSm} - A_4 (V_{\text{gds}}^3 + 2V_{\text{cut}}^3 - 3V_{\text{cut}}^2 V_{\text{gds}})}{(V_{\text{cut}} - V_{\text{gds}})^2} \quad (6)$$

$$A_6 = -3A_4 V_{\text{cut}}^2 - 2A_5 V_{\text{cut}} \quad (7)$$

$$A_7 = -A_4 V_{\text{cut}}^3 - A_5 V_{\text{cut}}^2 - A_6 V_{\text{cut}}. \quad (8)$$

The meanings of the physical parameters are given in [10] (with the exception of  $I_{DSm}$ ).  $I_{DSm}$  is the value of  $I_S$  for  $V_{SG} = V_{\text{gds}}$ .  $V_{\text{gds}}$  is the value of  $V_{SG}$  at which the drain conductance,  $g_d$ , is maximum. [Explanation:  $g_d$  approaches zero as  $V_{SG}$  approaches both  $(-V_F)$  (open channel) and  $V_{SG} = V_{\text{cut}}$  (cutoff), so there has to be a maximum for  $g_d$  at some value,  $V_{\text{gds}}$ , such that  $-V_F < V_{\text{gds}} < V_{\text{cut}}$ .] Expression (2) is a better approximation for  $I_S$  and includes five regions, rather than the four regions in the "old" model.

The physical meanings of  $m$  and  $V_S$  are determined by calculating the drain conductance by differentiating (1):

$$g_d = \frac{\partial I_{\text{con}}}{\partial V_{DS}} = G_{d_0} (1 + mV_{DS}) \left[ 1 - \tanh^2 \left( \frac{V_{DS}}{V_S} \right) \right] + G_{d_\infty} \tanh \left( \frac{V_{DS}}{V_S} \right) \quad (9)$$

where

$$G_{d_0} = I_S / V_S \quad (10)$$

$$G_{d_\infty} = mI_S. \quad (11)$$

From (9) it is obvious that  $G_{d_0}$  is the value of  $g_d$  for  $V_{DS} = 0$ , namely, the initial slope of the  $I$ - $V$  curve.  $G_{d_0}$  is a function of  $V_{SG}$ . The suggested approximation for  $G_{d_0}$  is

$$G_{d_0} = G_{d_{00}} \left[ 1 - \sqrt{\frac{V_{SG} + \phi}{V_{\text{cut}} + \phi}} \right] / \left[ 1 - \sqrt{\frac{\phi}{V_{\text{cut}} + \phi}} \right] \quad (12)$$

where  $\phi$  is the built-in potential of the gate junction ( $\approx 0.8$  V).  $G_{d_0}$  is proportional to the free channel height.  $G_{d_{00}}$  is the value of  $G_{d_0}$  for  $V_{SG} = 0$ .  $V_S$  is calculated from (10) once  $G_{d_0}$  and  $I_S$  are known.

From (9) it is obvious that  $G_{d_\infty}$  is the value of  $g_d$  for  $V_{DS} \rightarrow \infty$ .  $G_{d_\infty}$  is a function of  $V_{SG}$ . The suggested approximation for  $G_{d_\infty}$  is a polynomial expression identical to that of  $g_{ds}$  in [10, eq. (7)]. Once  $G_{d_\infty}$  and  $I_S$  are known,  $m$  is calculated from (11).

### C. Diode Characterization

The gate-source and gate-drain junctions are simulated in Fig. 1 by the pair of diodes. In the large-signal simulations the diodes are characterized by the following equation:

$$I_{\text{diode}} = I^* (e^{\beta V_{\text{diode}}} - 1 - e^{-\beta(V_{\text{diode}} + V_B)}) \quad (13)$$

$$\beta = \frac{q}{kT} = 40 \quad (\text{at room temperature}) \quad (14)$$

where  $V_B$  is the avalanche breakdown voltage.  $I^*$  is generally not known; however, due to the exponential dependence on  $V_{\text{diode}}$  its exact value is not very important, and may be taken in the range of several nA. Equation (13) is basically the standard diode equation with the addition of a term representing the avalanche breakdown. The effect of "gradual avalanche" as described for example by Curtice [12] is not currently included in the diode model.

## III. SIMULATION RESULTS

The accuracy and usefulness of the improved model are demonstrated in this section by presenting calculated versus measured data. The types of data presented are dc  $I$ - $V$  curves, small-signal scattering parameters, and large-signal simulation results.

The device chosen is the HMF1200 by HARRIS. This is a 0.5 W power device useful up to 16 GHz. It has 0.5  $\mu\text{m}$  gate length, and is used for medium power applications. For this particular device, the electrical parameters used to characterize it by the improved analytical model are presented in Table I. The meaning of each of these parameters is explained in [10] with the necessary changes presented in Section II, above.

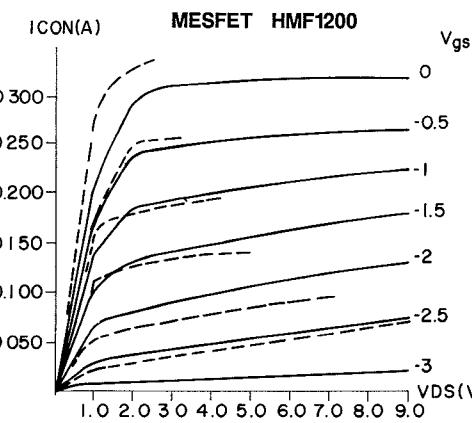

The dc  $I$ - $V$  curves of the device are presented in Fig. 2 (calculated—solid line; measured—dashed line). The measured  $I$ - $V$  curves of a power MESFET always include a region of negative slope. This slope does not represent

TABLE I

## MESFET HMF1200 DEVICE PARAMETERS TABLE

|    |                                      |   |        |      |

|----|--------------------------------------|---|--------|------|

| 1  | FORWARD CONDUCTION VOLTAGE (VF)      | : | .50    | VOLT |

| 2  | CUTOFF VOLTAGE (VCUT)                | : | 3.50   | VOLT |

| 3  | VSG FOR MAX GDS (VGDSM)              | : | 2.00   | VOLT |

| 4  | BUILT-IN POTENTIAL (PHI)             | : | .80    | VOLT |

| 5  | DEVICE MAX CURRENT (CURON)           | : | 430.00 | MA   |

| 6  | DEVICE CURRENT FOR VSG=0 (CURDSS)    | : | 340.00 | MA   |

| 7  | DEVICE CURRENT FOR VSG=VGDSM(CURDSM) | : | 70.00  | MA   |

| 8  | GM FOR VSG=0                         | : | 160.00 | MMHO |

| 9  | GD VALUE FOR VSG=VDS=0 (GDOO)        | : | 370.00 | MMHO |

| 10 | GD VALUE FOR VSG=VGDSM (GDSM)        | : | 8.00   | MMHO |

| 11 | GVSG VALUE FOR VSG=0 (CO)            | : | 1.793  | PF   |

| 12 | GVDS VALUE FOR VDS=VSG=0 (CMO)       | : | 0.4051 | PF   |

| 13 | (-DVSG) VALUE FOR LARGE VDS (CMAX)   | : | 0.0089 | PF   |

| 14 | DVDS VALUE FOR LARGE VDS (CH)        | : | 0.1372 | PF   |

| 15 | DVDS VALUE FOR VDS=0 (CL)            | : | 0.0443 | PF   |

| 16 | GVDS VALUE FOR LARGE VDS (CK)        | : | 0.0014 | PF   |

## MESFET HMF1200 PACKAGE/CIRCUIT PARAMETERS:

|    |                                          |   |          |             |

|----|------------------------------------------|---|----------|-------------|

| 1  | SOURCE INDUCTANCE (SIND)                 | : | 2.27E-02 | NANOHENRIES |

| 2  | GATE INDUCTANCE (GIND)                   | : | 8.62E-02 | NANOHENRIES |

| 3  | DRAIN INDUCTANCE (DIND)                  | : | 2.14E-01 | NANOHENRIES |

| 4  | PARASITIC INPUT CAPACITANCE (SCAPIN)     | : | 1.17E-03 | PICOFARADS  |

| 5  | PARASITIC OUTPUT CAPACITANCE (SCAPO)     | : | 3.17E-03 | PICOFARADS  |

| 6  | GATE PAD CAPACITANCE (CPADG)             | : | 2.58E-01 | PICOFARADS  |

| 7  | DRAIN PAD CAPACITANCE (CPADD)            | : | 2.78E-01 | PICOFARADS  |

| 8  | DRAIN TO GATE PAD CAPACITANCE (CAPDG)    | : | 1.08E-01 | PICOFARADS  |

| 9  | GATE METALLIZATION RESISTANCE (RG)       | : | 0.068    | OHMS        |

| 10 | SUBSTRATE LEAKAGE RESISTANCE (RSUBST)    | : | 1.00E+20 | OHMS        |

| 11 | SOURCE METALLIZATION RESISTANCE (RSCONT) | : | 0.000    | OHMS        |

| 12 | DRAIN METALLIZATION RESISTANCE (RDCONT)  | : | 0.000    | OHMS        |

| 13 | SOURCE BULK RESISTANCE (RSS)             | : | 0.589    | OHMS        |

| 14 | DRAIN BULK RESISTANCE (RSD)              | : | 0.881    | OHMS        |

| 15 | CHANNEL TIME DELAY (TAU)                 | : | 4.150    | PS          |

Fig. 2. Calculated (—) and measured (----) dc curves for HMF1200.

negative resistance. It has long been known that this phenomenon is due to thermal effects, since the thermal time constant of the MESFET is much smaller than the measurement time (even pulsed measurement). For the HMF1200 the negative slope exists for  $V_{gs} > -1$  V. To avoid confusion the negative slope is not included in Fig.

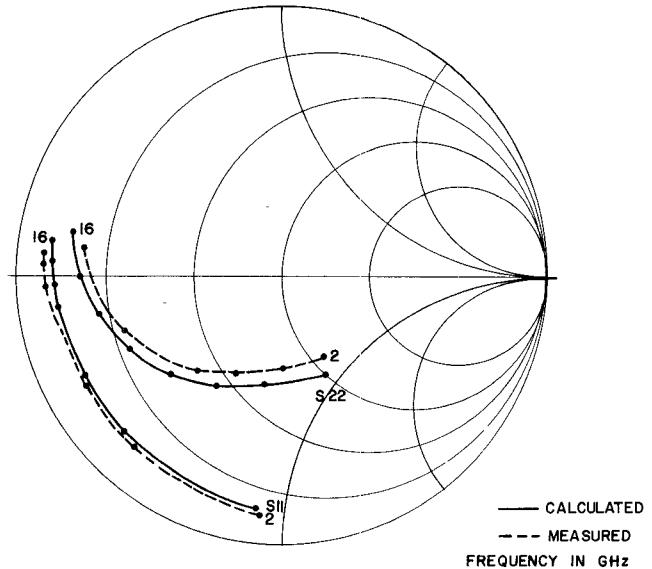

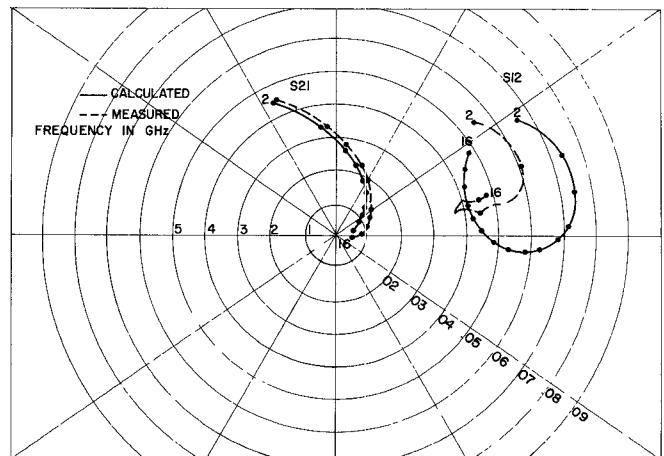

Fig. 3.  $S_{11}$  and  $S_{22}$  for HMF1200.Fig. 4.  $S_{12}$  and  $S_{21}$  for HMF1200.

2, and the curves are stopped at the point where the negative slope starts. It can be seen from Fig. 2 that good correlation exists between calculated and measured dc curves. Thermal effects can be included in small-signal analysis by assuming some monotonic decrease of  $I_{con}$  with dc power dissipation, and thus correcting the dc point. For large-signal analysis, a similar approach can be adopted. However, here the average power dissipation must be considered. In this paper such a correction was not performed.

The small-signal scattering parameters of the device are presented in Figs. 3 and 4. In Fig. 3,  $S_{11}$  and  $S_{22}$  are presented and in Fig. 4  $S_{12}$  and  $S_{21}$  are presented (calculated—solid line; measured—dashed line). Note the different scales for  $S_{12}$  and  $S_{21}$  in Fig. 4. The  $S$  parameters are for the bias point  $V_{DS} = 8$  V,  $V_{SG} = 1.5$  V ( $\approx 50$  percent  $I_{DSS}$ ). The measured data are taken from the manufacturer's data sheet. Since the HMF1200 is a power MESFET, the large-signal simulation chosen is that of a power amplifier. The amplifier is composed of the device

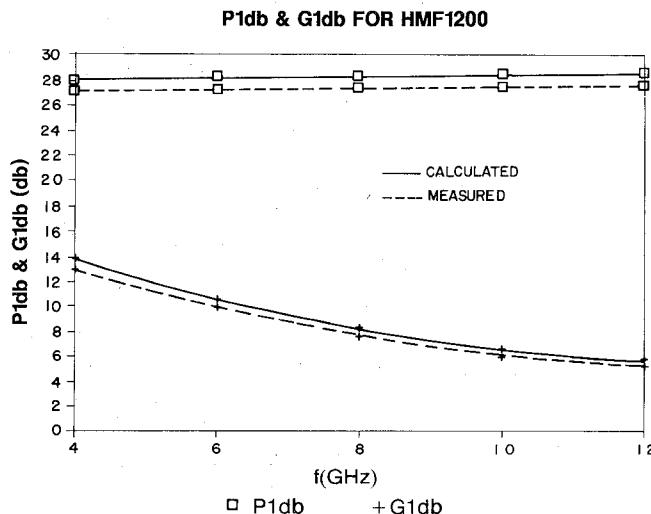

Fig. 5. 1 dB compression and associated gain for HMF1200 amplifier.

loaded by an optimum power load at the drain and is excited by a power source conjugately matched at the gate. The optimum power load is calculated as outlined in [13]. The input impedance with that load is calculated and the power source is conjugately matched.

The above large-signal network is analyzed using the harmonic balance approach, which is the most useful and efficient method for steady-state applications [1]–[3], [10], [12]. The analysis was performed for the bias point  $V_{DS} = 8$  V,  $V_{SG} = 1.3$  V ( $\approx 60$  percent  $I_{DSS}$ ), which is recommended for maximum output power. The analysis was repeated for several power levels up to and beyond the 1 dB compression point and for the frequencies 4, 6, 8, 10, and 12 GHz. The computer program can handle up to eight harmonics in the harmonic balance scheme. However, it was found that three harmonics are sufficient for simulating the network, even beyond the 1 dB compression. Of course, for deep saturation more harmonics are needed. The program runs on an IBM-PC/AT and is very efficient. A typical run takes about 4 seconds for low power levels and increases to 20–25 seconds in the vicinity of the 1 dB compression point.

The results of the simulations are presented in the form of the two graphs in Fig. 5. One graph presents the 1 dB compression point and the other the associated gain versus frequency. The calculated data are presented in the solid line and measured data (from the manufacturer's data sheet) are presented in the dashed line. It can be seen that the calculated gain and power are slightly greater than the measured values. This is expected, since the matching networks have some loss, which is not included in the calculation. The loss in the input matching network may be appreciable due to the large transformation ratio (the input impedance to the device is only a few ohms).

#### IV. CONCLUSION

In this paper an improved analytical ac large-signal model for a MESFET is presented. The new model is an upgrading of a previously presented model. The improve-

ment is basically in the expressions for the conduction current. Simulation results are presented and compared to measured data.

#### REFERENCES

- [1] V. Rizzoli and A. Lipparini, "A general-purpose program for nonlinear microwave circuit design," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, pp. 762–770, Sept. 1983.

- [2] R. J. Gilmore and F. J. Rosenbaum, "Modelling of nonlinear-distortion in GaAs MESFETs," in *1984 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 430–431.

- [3] R. Gilmore, "Design of a novel FET frequency doubler using a harmonic balance algorithm," in *1986 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 585–588.

- [4] J. Dreifuss, A. Madjar, and A. Bar-Lev, "A novel method for the analysis of microwave two-port active mixers," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-33, pp. 1241–1244, Nov. 1985.

- [5] A. Madjar, "Analysis of microwave FET oscillator using an efficient computer model for the device," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 915–917, June 1982.

- [6] V. Rizzoli and A. Neri, "State of the art and present trends in nonlinear microwave CAD techniques," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 343–365, Feb. 1988.

- [7] K. S. Kundert *et al.*, "Applying harmonic balance to almost-periodic circuits," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 366–378, Feb. 1988.

- [8] A. Madjar and F. J. Rosenbaum, "An ac large signal model for the GaAs MESFET," Final Rep. Contract N00014-78-C-0256, Dept. Electrical Engineering, Washington University, St. Louis, MO, Aug. 1979.

- [9] A. Madjar and F. J. Rosenbaum, "A large signal model for the GaAs MESFET," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-29, pp. 781–788, Aug. 1981.

- [10] A. Madjar, "A fully analytical ac large-signal model of the GaAs MESFET for nonlinear network analysis and design," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 61–67, Jan. 1988.

- [11] D. R. Green, Jr., and F. J. Rosenbaum, "Performance limits on GaAs FET large and small signal circuits," Tech. Rep. NRL-81-1, Contract N00014-80-0318, Dept. Electrical Engineering, Washington University, St. Louis, MO, Oct. 1981.

- [12] W. R. Curtice, "GaAs MESFET modeling and nonlinear CAD," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 220–230, Feb. 1988.

- [13] HARRIS Application Note 2: "Output power match for  $P_{1db}$ : Power FET chips," Feb. 1987.

†

**Asher Madjar** (S'77–M'79–SM'83) received the B.Sc. and M.Sc. degrees in electrical engineering from the Technion—Israel Institute of Technology in 1967 and 1969, respectively, and the D.Sc. degree in electrical engineering from Washington University, St. Louis, MO, in 1979.

Since 1969 he has been working for RAFAEL—MOD Israel and teaching at the Technion. His fields of interest include microwave components and subsystems. He does research and development work on passive components, mixers, amplifiers, switches, and sources. He served as head of the MIC laboratory for three years. Since 1976 he has been involved in the large-signal modeling of GaAs MESFETs, and he developed a large-signal model for use in network analysis and design (D.Sc. thesis). In the last few years he has been involved in nonlinear circuit simulation, both in the time domain and in the frequency domain (harmonic balance), and has published several papers on this topic. Since 1982 he has served as chief scientist of a microwave department, and instructs graduate students at the Technion. He is currently involved in the design of microwave monolithic circuits.

Dr. Madjar has been serving for several years as AP/MMT joint chapter chairman in Israel. Since 1985 he has served as IEEE Israel section secretary.